|

24 |

GameFSMの改良 (8) |

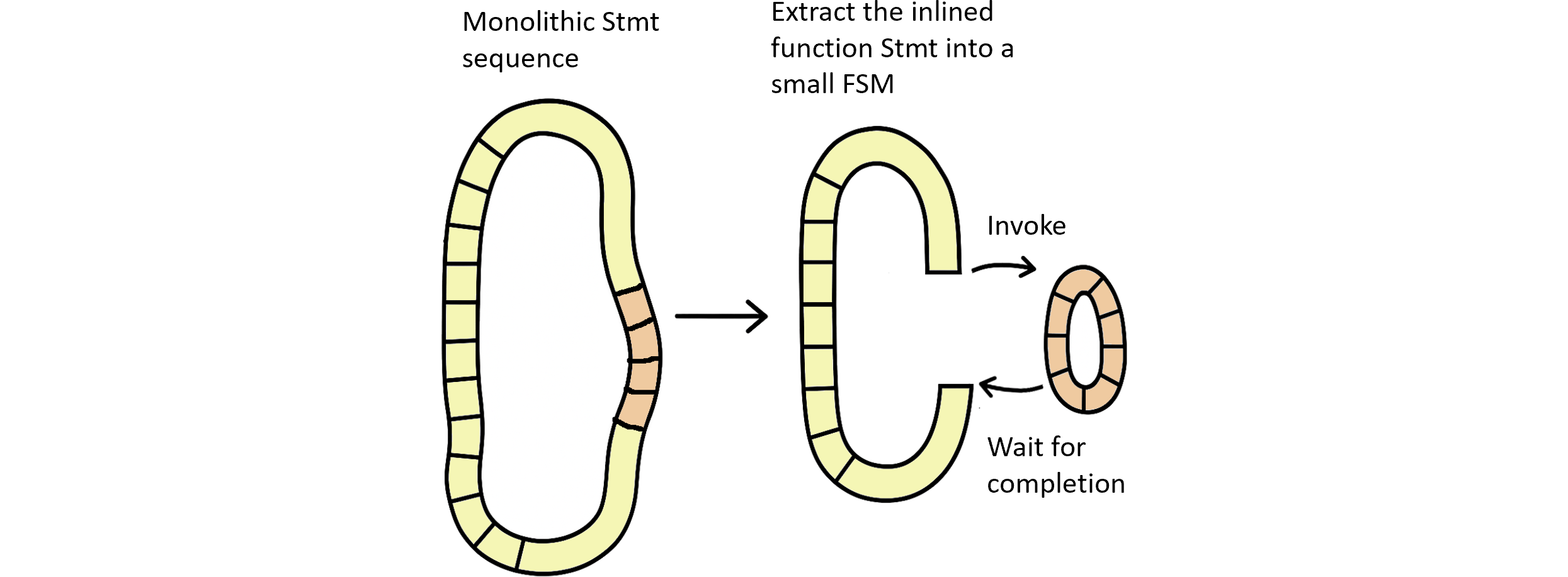

従来のcopyAreaをStmtで記述して呼び出す方式(変更前)と今回の切り出した小FSMを起動する方式(変更後)の模式図です。図では一回だけですが、n回呼び出されることを考えるとその機能だけでは物量が1/nに減少します。さらにスケジューリングも楽になります。

従来と今回の2つのbsvとverilogの結果比較です。

| 画面アクセス改良前後 | 前 | 後 | 比較 | |

|---|---|---|---|---|

| BSV合成 | ソース行数[行] | 52,138 | 60,756 | 17%増 |

| コンパイル時間 | 16:27 | 2:10 | ▲87% | |

| Verilog合成 | ファイルサイズ[KB] | 29,156 | 8,398 | ▲71% |

| 合成時間 | 1:47 | 1:00 | ▲44% | |

| Vivado LUT数 | 7,212 | 5,901 | ▲18% | |

| Vivado FF数 | 1,821 | 1,812 | ▲0.5% | |

BSVソースはスイッチによりオリジナルと小FSM方式を出力し分けるように両方のコードが入っているため却って増大しています。

なお、前記事のfunction _BLIT()においてnoActionをコメントにしている場合の数値であり、その代わりに変数競合の警告がでます。実際には問題ないので警告offにしていますが、警告を消す場合はこのnoActionを入れる必要があります。ただしその分コンパイル時間、物量共増大します。

Leave a Comment